隨著計算機技術(shù)的飛速發(fā)展,理解中央處理器(CPU)的工作原理已成為計算機愛好者和專業(yè)人士的重要課題。《CPU設(shè)計與實現(xiàn)》這一主題引領(lǐng)我們深入探索計算機系統(tǒng)的核心,揭示數(shù)據(jù)如何在電路中流動,指令如何被解析執(zhí)行,以及整個系統(tǒng)如何協(xié)同工作。

CPU設(shè)計基礎(chǔ)

CPU設(shè)計始于架構(gòu)選擇。常見的架構(gòu)包括精簡指令集(RISC)和復雜指令集(CISC),每種架構(gòu)在性能、功耗和復雜度上各有優(yōu)劣。設(shè)計者需明確CPU的目標應(yīng)用場景:是用于低功耗嵌入式設(shè)備,還是高性能計算服務(wù)器?在此基礎(chǔ)上,定義指令集架構(gòu)(ISA),包括數(shù)據(jù)格式、尋址模式和操作碼,這是CPU與軟件交互的橋梁。

設(shè)計過程中,邏輯電路是關(guān)鍵。從簡單的與門、或門到復雜的算術(shù)邏輯單元(ALU),每個組件都需優(yōu)化以提升效率。例如,ALU負責執(zhí)行算術(shù)和邏輯運算,其設(shè)計直接影響CPU的處理速度。控制單元負責解碼指令并協(xié)調(diào)數(shù)據(jù)流,確保各部件同步工作。

實現(xiàn)過程與技術(shù)

實現(xiàn)CPU涉及硬件描述語言(如Verilog或VHDL)的使用,通過代碼定義電路行為,再通過仿真工具驗證功能。現(xiàn)代FPGA(現(xiàn)場可編程門陣列)技術(shù)使得原型設(shè)計更加便捷,開發(fā)者可以在實際硬件上測試設(shè)計,而無需昂貴的ASIC制造。

在實現(xiàn)階段,流水線技術(shù)是提升性能的常用方法。通過將指令處理分成多個階段(如取指、解碼、執(zhí)行、寫回),CPU可以并行處理多條指令,顯著提高吞吐量。流水線也帶來數(shù)據(jù)沖突和分支預測等挑戰(zhàn),需要精心設(shè)計解決。

計算機系統(tǒng)與服務(wù)的整合

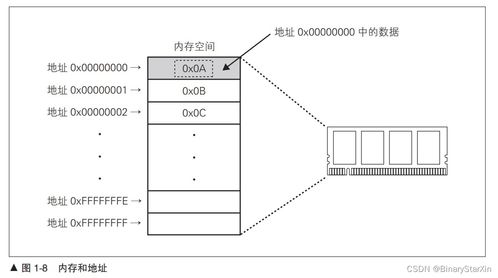

CPU是計算機系統(tǒng)的核心,但它并非孤立存在。它通過總線與內(nèi)存、存儲設(shè)備和外設(shè)交互,構(gòu)成完整的計算機系統(tǒng)。操作系統(tǒng)作為系統(tǒng)服務(wù)的管理者,調(diào)度CPU資源,處理中斷和異常,確保多任務(wù)環(huán)境下的穩(wěn)定運行。

例如,在服務(wù)器領(lǐng)域,CPU設(shè)計需考慮虛擬化支持,以運行多個虛擬機;在嵌入式系統(tǒng)中,低功耗和實時性則是首要目標。系統(tǒng)服務(wù)如進程管理、內(nèi)存分配和I/O操作,都依賴于CPU的高效執(zhí)行。因此,CPU設(shè)計者必須理解整體系統(tǒng)需求,實現(xiàn)軟硬件協(xié)同優(yōu)化。

實踐與學習路徑

對于初學者,從簡單CPU模型入手是理想起點。例如,設(shè)計一個8位CPU,支持基本指令如加法和跳轉(zhuǎn),可以幫助理解數(shù)據(jù)通路和控制邏輯。開源工具如Logisim提供圖形化仿真環(huán)境,降低入門門檻。隨著經(jīng)驗積累,可以逐步探索多核處理器、緩存設(shè)計和超標量架構(gòu)等高級主題。

CPU自制不僅是技術(shù)挑戰(zhàn),更是深入理解計算機系統(tǒng)的窗口。通過設(shè)計與實現(xiàn),我們不僅能掌握硬件原理,還能更好地優(yōu)化軟件性能,推動技術(shù)創(chuàng)新。無論您是學生、工程師還是愛好者,這一旅程都將帶來豐富的收獲。